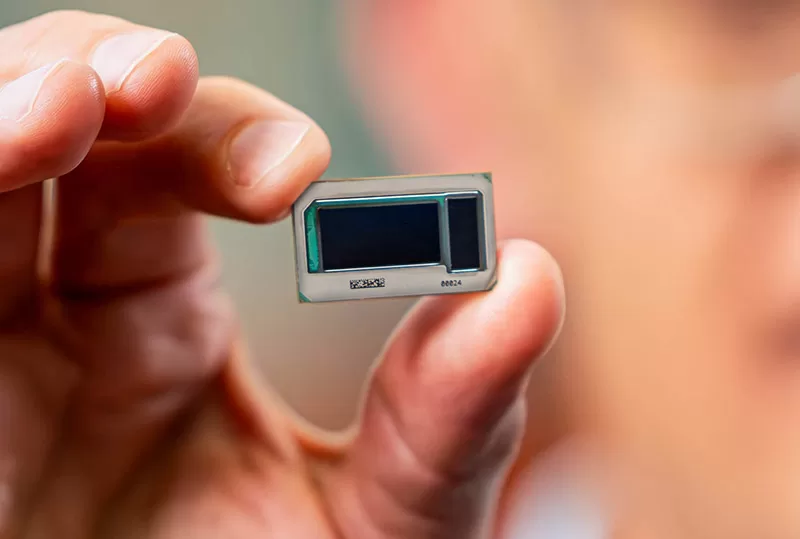

Intel presenta uno de los primeros sustratos de vidrio para el empaquetado avanzado de próxima generación, previsto para finales de esta década.

Este gran logro con sustratos de vidrio permitirá seguir ampliando el número de transistores en un encapsulado y avanzar en la Ley de Moore para ofrecer aplicaciones centradas en los datos.

En comparación con los sustratos orgánicos actuales, el vidrio ofrece propiedades distintivas como una planitud ultrabaja y una mayor estabilidad térmica y mecánica, lo que se traduce en una densidad de interconexión mucho mayor en un sustrato.

Estas ventajas permitirán a los arquitectos de chips crear paquetes de chips de alta densidad y alto rendimiento para cargas de trabajo intensivas en datos, como la inteligencia artificial (IA).

Los sustratos de vidrio para 2030

Intel está en vías de ofrecer al mercado soluciones completas de sustrato de vidrio en la segunda mitad de esta década, lo que permitirá al sector seguir avanzando en la Ley de Moore más allá de 2030.

A finales de la década, la industria de los semiconductores alcanzará probablemente sus límites en cuanto a la capacidad de escalar transistores en un encapsulado de silicio utilizando materiales orgánicos, que consumen más energía e incluyen limitaciones como la contracción y la deformación.

El escalado es crucial para el progreso y la evolución de la industria de los semiconductores, y los sustratos de vidrio son un paso viable y esencial para la próxima generación de semiconductores.

A medida que aumenta la demanda de ordenadores más potentes y la industria de semiconductores se adentra en la era heterogénea que utiliza múltiples “chiplets” en un encapsulado, será esencial mejorar la velocidad de señalización, la entrega de potencia, las normas de diseño y la estabilidad de los sustratos de encapsulado.

El vidrio el mejor aliado para la tecnología

Los sustratos de vidrio tienen unas propiedades mecánicas, físicas y ópticas superiores que permiten conectar más transistores en un encapsulado, lo que ofrece un mejor escalado y permite ensamblar complejos de chiplets más grandes (denominados “sistema en encapsulado”) en comparación con los sustratos orgánicos que se utilizan hoy en día. Los diseñadores de chips podrán empaquetar más chips (también llamados “chiplets”) en menos espacio dentro de un mismo encapsulado, lo que aumentará el rendimiento y la densidad con mayor flexibilidad y reducirá el coste total y el consumo de energía.

Los sustratos de vidrio se introducirán inicialmente en el mercado allí donde puedan aprovecharse al máximo: aplicaciones y cargas de trabajo que requieran paquetes de mayor factor de forma (por ejemplo, centros de datos, IA, gráficos) y capacidades de mayor velocidad.

Los sustratos de vidrio pueden tolerar temperaturas más elevadas, ofrecen un 50% menos de distorsión de patrones y tienen una planitud ultrabaja para mejorar la profundidad de enfoque en litografía, además de contar con la estabilidad dimensional necesaria para una superposición de interconexiones capa a capa extremadamente ajustada.

Gracias a estas propiedades, es posible multiplicar por 10 la densidad de interconexión en los sustratos de vidrio. Además, la mejora de las propiedades mecánicas del vidrio permite fabricar paquetes de formato ultra grande con rendimientos de montaje muy elevados.

La tolerancia de los sustratos de vidrio a temperaturas más elevadas también ofrece a los arquitectos de chips flexibilidad a la hora de establecer las reglas de diseño para el suministro de energía y el enrutamiento de señales, ya que les permite integrar a la perfección interconexiones ópticas, así como incrustar inductores y condensadores en el vidrio a temperaturas de procesamiento más elevadas.

Esto permite mejores soluciones de suministro de energía al tiempo que se consigue la señalización de alta velocidad que se necesita a mucha menor potencia. Estas numerosas ventajas acercan a la industria a la posibilidad de escalar 1 billón de transistores en un paquete para 2030.